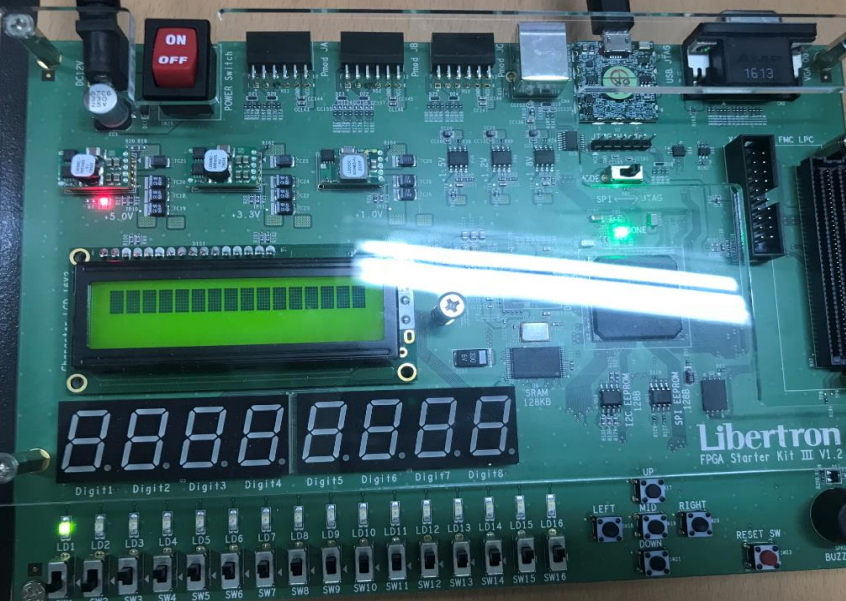

【FPGA】基本实验步骤演示 | Verilog编码 | 运行合成 | 设备/引脚分配 | 综合/实施 | 设备配置 | 以最简单的逻辑非为例

写在前面:本章的目的是让你理解与门、或门和非门的行为,并使用 Verilog 语言实现多输入与门、或门和非门。在生成输入信号之后,你需要通过模拟来验证这些门的操作,并使用 FPGA 来验证 Verilog 实现的电路的行为。0x00 引入:与门、或门与非门构成数字系统电路的最基本元素,以集成电路的形式实现逻辑代数中0和1的运算,作为这些逻辑代数基础的门有与门、或门、非门等,它们的组合可以生成多种....

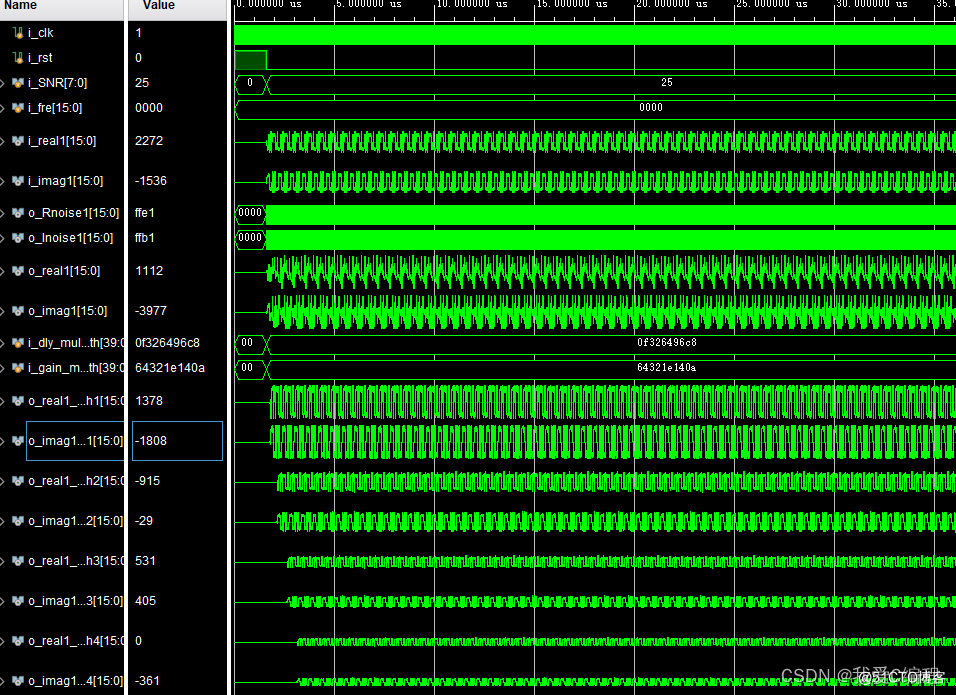

m基于FPGA的多径信道模拟verilog实现,包含testbench,可配置SNR,频偏,多径增益和多径延迟

1.算法仿真效果其中Vivado2019.2仿真结果如下: 2.算法涉及理论知识概要 瑞利分布是一个均值为0,方差为σ²的平稳窄带高斯过程,其包络的一维分布是瑞利分布。其表达式及概率密度如图所示。瑞利分布是最常见的用于描述平坦衰落信号接收包络或独立多径分量接受包络统计时变特性的一种分布类型。两个正交高斯噪声信号之和的包络服从瑞利分布。 瑞利衰落能有效描述存在能够大量散射无线电信号的障碍物的...

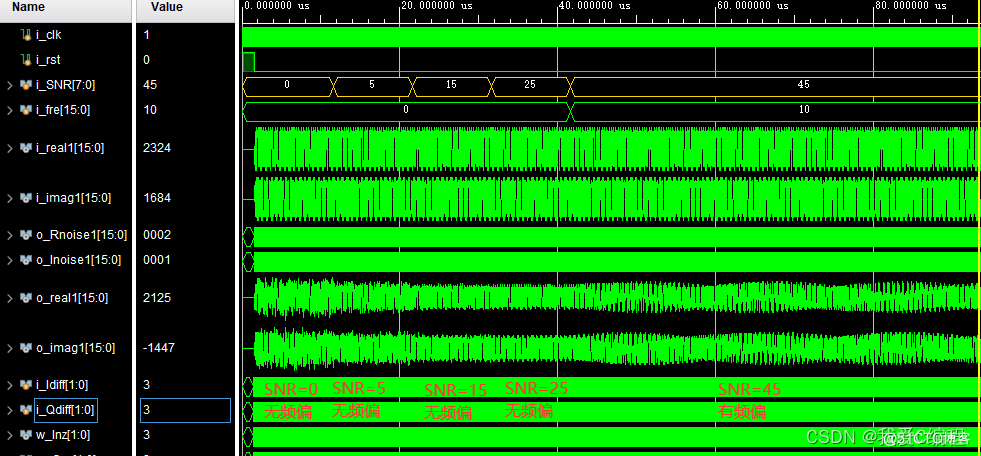

m基于FPGA的高斯白噪声信道模拟系统verilog实现,包含testbench,可以配置不同的SNR和频偏

1.算法仿真效果vivado2019.2仿真结果如下: SNR=0db,无频偏 SNR=5db,无频偏 SNR=25db,无频偏 SNR=45db,带频偏 2.算法涉及理论知识概要 高斯白噪声信道在通信系统中具有重要意义,模拟此类信道有助于评估系统性能。本文提出的FPGA实现系统可以灵活地模拟不同信道条件,为通信系统的设计和测试提供有力支持。 本系统的设计分为以下几...

m基于FPGA的数据串并并串转换系统verilog实现,包含testbench,可以配置并行数量

1.算法仿真效果 本系统进行了两个平台的开发,分别是: Vivado2019.2 Quartusii18.0+ModelSim-Altera 6.6d Starter Edition 其中Vivado2019.2仿真结果如下: 分别进行2路,4路,8路,16路并行串行转换 Quartusii18.0+ModelSim-Altera 6.6d Starter Edition的测试结...

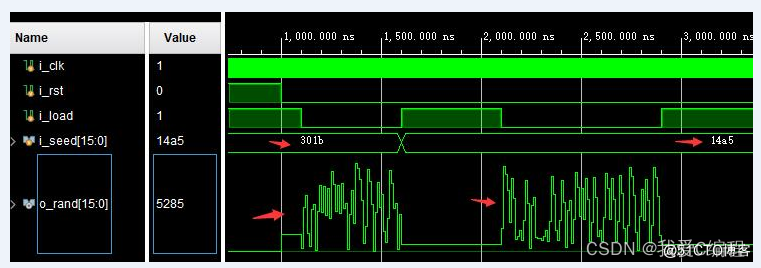

基于FPGA的LFSR16位伪随机数产生算法实现,可以配置不同的随机数种子和改生成多项式,包含testbench

1.算法仿真效果vivado2019.2仿真结果如下: 2.算法涉及理论知识概要 LFSR(线性反馈移位寄存器)提供了一种在微控制器上快速生成非序列数字列表的简单方法。生成伪随机数只需要右移操作和 XOR 操作。LFSR 完全由其多项式指定。例如,6千-次多项式与每个项存在用方程 x 表示6+ x5+ x4+ x3+ x2+ x + 1。有 2 个(6 - 1)= 32 个这种大小的不同可...

Xilinx FPGA SPI配置芯片都支持哪些型号

众所周知,大多数FPGA芯片都会外挂一片Flash芯片,用于存储FPGA的程序文件。FPGA程序下载分为两种,一种是片上调试,程序会下载到内部RAM空间,掉电程序会丢失。另一种是程序固化,程序会下载到外部Flash芯片,一般采用的是SPI接口的Flash芯片,包括1/4/8/16位数据宽度,但不是所有型号的SPI Flash芯片都支持作为FPGA的配置芯片。本文以Xilinx FPGA为例,介绍....

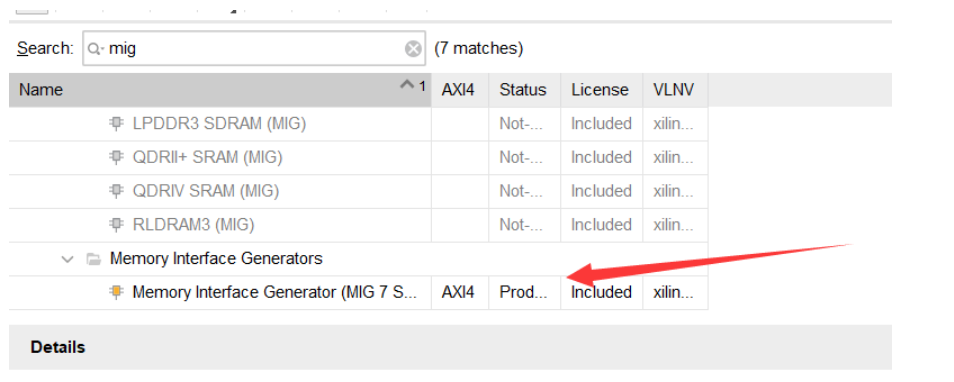

FPGA - DDR IP配置

写在前面本文主要对DDR IP核进行相关配置,完成DDR IP核的配置工作。配置步骤点击 IP Catalog,Search 框中输入 memory interface, 查找到相关的DDR的 IP 核。双击 IP 核名称打开 DDR3 SDRAM IP 核调取界面,该界面主要是总结了所选芯片的型号等。 点击next,此可以按照个人喜好定义器件的名称,也可以选择 DDR3 控制器的个数,我们的器....

本页面内关键词为智能算法引擎基于机器学习所生成,如有任何问题,可在页面下方点击"联系我们"与我们沟通。

FPGA云服务器您可能感兴趣

- FPGA云服务器设置

- FPGA云服务器系统开发

- FPGA云服务器信道

- FPGA云服务器解调

- FPGA云服务器误码

- FPGA云服务器调制

- FPGA云服务器psk

- FPGA云服务器统计

- FPGA云服务器模块

- FPGA云服务器snr

- FPGA云服务器testbench

- FPGA云服务器verilog

- FPGA云服务器matlab

- FPGA云服务器测试

- FPGA云服务器验证

- FPGA云服务器文件

- FPGA云服务器驱动

- FPGA云服务器辅助

- FPGA云服务器实验

- FPGA云服务器算法

- FPGA云服务器系统

- FPGA云服务器教程

- FPGA云服务器图像

- FPGA云服务器程序

- FPGA云服务器技术

- FPGA云服务器阿里云

- FPGA云服务器芯片

- FPGA云服务器逻辑

- FPGA云服务器开发

- FPGA云服务器结构

云服务器ECS

云服务器ECS是一种安全可靠、弹性可伸缩的IaaS级云计算服务。在这里你可以获取最新的ECS产品资讯、最前沿的技术交流以及优惠活动等信息,加速自己的技术成长。

+关注