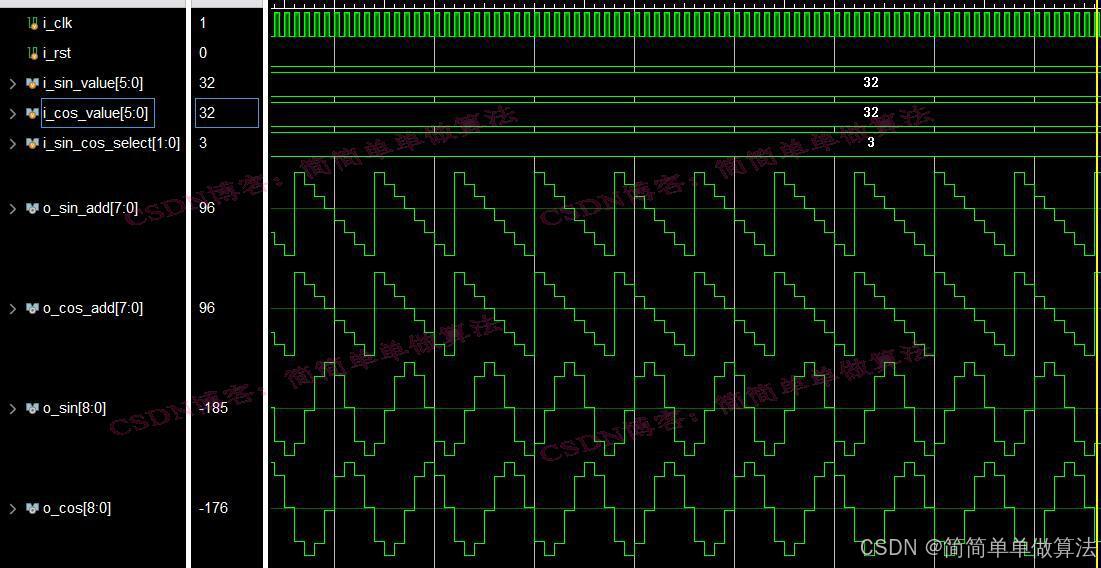

基于FPGA的直接数字频率合成器verilog实现,包含testbench

1.算法运行效果图预览(完整程序运行后无水印) 2.算法运行软件版本vivado2019.2 3.部分核心程序(完整版代码包含详细中文注释和操作步骤视频) always @(posedge i_clk)//时钟上边沿触发 begin if(i_rst)//系统复位 begin o_sin_add<=8'...

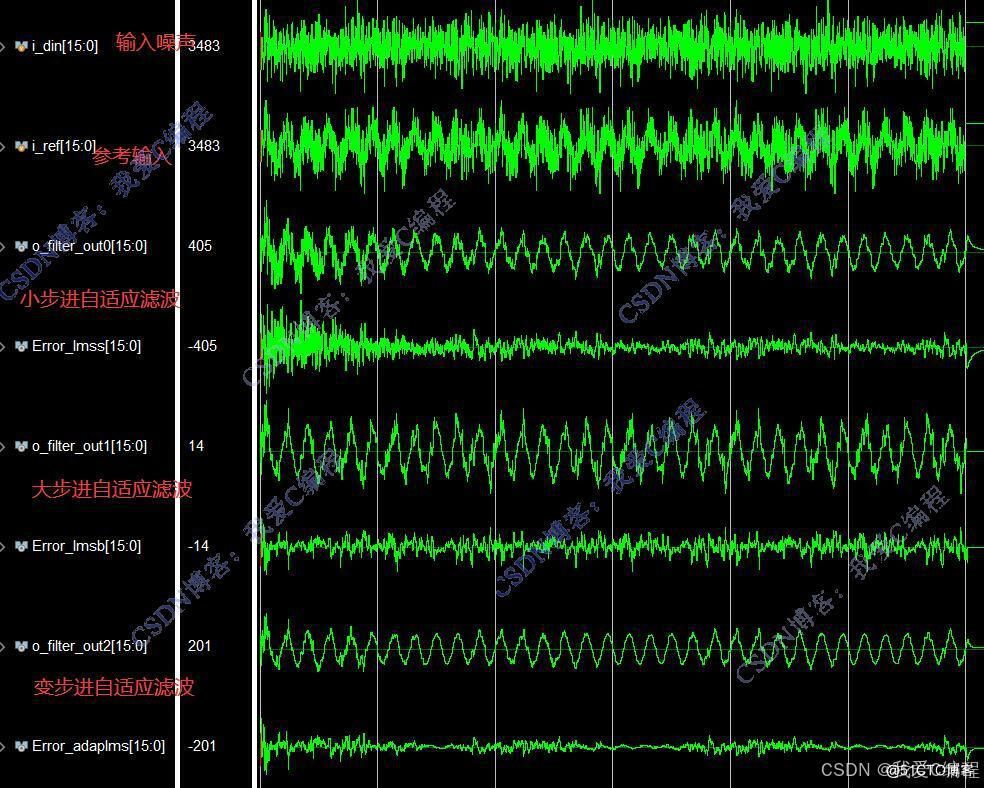

基于FPGA的变步长LMS自适应滤波器verilog实现,包括testbench

1.算法仿真效果vivado2022a仿真结果如下(完整代码运行后无水印): 仿真操作步骤可参考程序配套的操作视频。 2.算法涉及理论知识概要 自适应滤波器一般由两个主要部分组成:一是可调整的数字滤波器,其系数可以根据输入信号和期望信号进行调整;二是自适应算法,用于更新滤波器的系数。常...

基于FPGA的MSK调制解调系统verilog开发,包含testbench,同步模块,高斯信道模拟模块,误码率统计模块

1.算法仿真效果本程序系统是《m基于FPGA的MSK调制解调系统verilog开发,并带FPGA误码检测模块和matlab仿真程序》的的升级。 升级前原文链接 增加了完整的AWGN信道模型的FPGA实现,可以在testbench里面设置SNR,分析不同SNR对应的FPGA误码率情况。 vivado2019.2仿真结果如下(完整代码运行后无水印): 设置SNR=0: 设置SNR=5:...

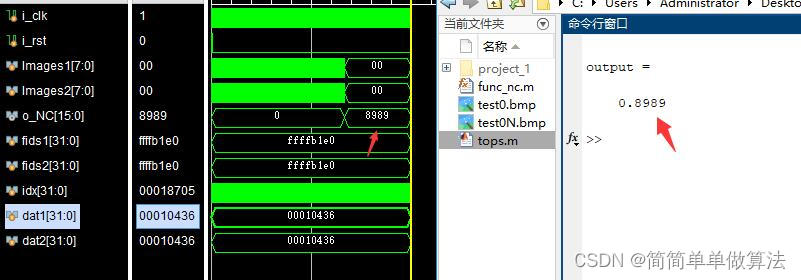

基于FPGA的NC图像质量评估verilog实现,包含testbench和MATLAB辅助验证程序

1.算法运行效果图预览vivado2019.2和matlab2022a测试,结果如下: 2.算法运行软件版本vivado2019.2 matlab2022a 3.算法理论概述 图像质量的含义包括图像的逼真度和图像的可读懂性。所谓图像的逼真度是指被评价图像与标准图像的偏离程度,偏差越小,逼真度越高。而图像的可读懂性是指由图像能向人或机器提供信息的能力,它不仅与图像系统的应用要求有...

m基于FPGA的MPPT最大功率跟踪算法verilog实现,包含testbench

1.算法仿真效果其中Vivado2019.2仿真结果如下: 使用matlab进行显示如下: 2.算法涉及理论知识概要 在太阳能光伏系统中,最大功率点跟踪(Maximum Power Point Tracking, MPPT)是提高能量转换效率的关键技术之一。爬山法(Hill Climbing Algorithm, HCA)作为最直观和基础的MPPT算法之一,因其简单易实现而被广泛研究...

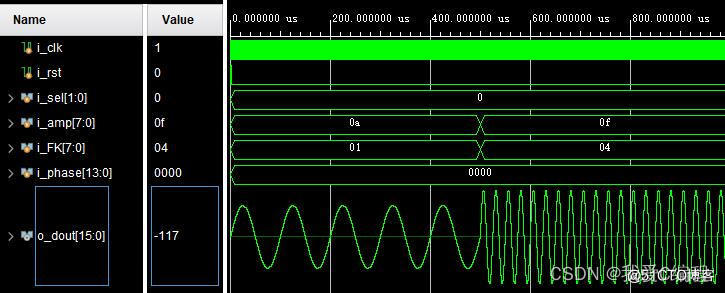

m基于FPGA的多功能信号发生器verilog实现,包含testbench,可以调整波形类型,幅度,频率,初始相位等

1.算法仿真效果vivado2019.2仿真结果如下: 输出正弦,并改变幅度,频率等。 输出方波,并改变幅度,频率等。 输出锯齿波,并改变幅度,频率等。 输出三角波,并改变幅度,频率等。 2.算法涉及理论知识概要 DDS(Direct Digital Synthesis,直接数字频率合成)技术是一种通过高性能数字计数器和查找表技术生成高精度、灵活可控的模拟信号的手段。DDS...

m基于FPGA的多通道FIR滤波器verilog实现,包含testbench测试文件

1.算法仿真效果VIVADO2019.2仿真结果如下: 系统RTL结构如下: 2.算法涉及理论知识概要 多通道FIR(Finite Impulse Response)滤波器是一种在数字信号处理中广泛应用的线性时不变滤波技术,尤其适用于多通道音频、视频、图像等多维数据的处理。 单通道FIR滤波器可由其单位脉冲响应(Impulse Response, IR)]h[n] 定义,其长度为...

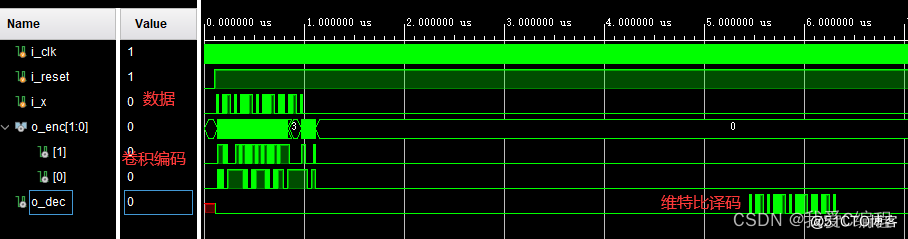

m基于FPGA的217卷积编码维特比译码verilog实现,包含testbench不使用IP核

1.算法仿真效果Vivado2019.2 编码部分: 译码部分输出: RTL图: 2.算法涉及理论知识概要2.1 卷积编码 卷积编码是一种前向纠错编码方式,特别适用于无线通信和其他信道条件恶劣的应用场景。它主要通过卷积算子将信息序列映射成冗余度更高的码字序列。典型的卷积编码器由两个移位寄存器和一个加法器构成,遵循一定的生成多项式进行编码。 设信息序列是 u(n),卷积...

m基于FPGA的电子钟verilog实现,可设置闹钟,包含testbench测试文件

1.算法仿真效果本系统进行Vivado2019.2平台的开发,测试结果如下所示: 2.算法涉及理论知识概要 电子钟是现代生活中常见的计时工具,其准确性和功能性不断提高。基于FPGA的电子钟设计不仅具有灵活的可定制性,还能通过集成其他功能(如闹钟)来增强实用性。Verilog作为一种广泛使用的硬件描述语言,为FPGA设计提供了强大的描述和仿真能力。FPGA是一种可通过编程配置实现特定功能的集...

m基于FPGA的Alamouti编码verilog实现,包含testbench测试文件

1.算法仿真效果 本系统进行了Vivado2019.2平台的开发,结果如下: 2.算法涉及理论知识概要 在无线通信领域,多天线技术是提高系统容量和可靠性的关键手段之一。Alamouti编码是空时编码(STC)的一种,它为两发射天线的系统提供了一种全速率、全分集的简单编码方案。而空频分组编码(SFBC)则是Alamouti编码在频域的一种扩展,用于在正交频分复用(OFDM)等系统中获得类似...

本页面内关键词为智能算法引擎基于机器学习所生成,如有任何问题,可在页面下方点击"联系我们"与我们沟通。

FPGA云服务器verilog相关内容

- FPGA云服务器算法verilog matlab

- FPGA云服务器图像插值verilog验证

- FPGA云服务器算法verilog

- FPGA云服务器verilog matlab验证

- FPGA云服务器verilog测试

- FPGA云服务器verilog验证

- FPGA云服务器自适应verilog testbench

- FPGA云服务器滤波器verilog testbench

- FPGA云服务器滤波器verilog

- FPGA云服务器信号发生器verilog

- FPGA云服务器调制解调系统verilog

- FPGA云服务器verilog同步

- FPGA云服务器msk调制解调系统verilog模块

- FPGA云服务器verilog开发testbench

- FPGA云服务器verilog开发

- FPGA云服务器调制解调系统verilog testbench

- FPGA云服务器入门verilog

- FPGA云服务器verilog hdl

- FPGA云服务器fft verilog

- FPGA云服务器verilog testbench程序

- FPGA云服务器verilog程序

- FPGA云服务器算法verilog testbench

- FPGA云服务器信号verilog包含testbench

- FPGA云服务器图像verilog tb验证

- FPGA云服务器fir verilog

- FPGA云服务器verilog testbench测试

- FPGA云服务器verilog testbench文件

- FPGA云服务器译码verilog testbench

- FPGA云服务器verilog testbench ip

- FPGA云服务器verilog包含testbench测试文件

FPGA云服务器更多verilog相关

- FPGA云服务器编译码verilog

- FPGA云服务器编译码verilog testbench文件

- FPGA云服务器ip verilog testbench

- FPGA云服务器verilog文件

- FPGA云服务器图像verilog

- FPGA云服务器变换verilog testbench

- FPGA云服务器信号verilog testbench

- FPGA云服务器信号verilog

- FPGA云服务器滤波verilog

- FPGA云服务器verilog ip

- FPGA云服务器调制verilog

- FPGA云服务器解调verilog testbench

- FPGA云服务器调制解调verilog

- FPGA云服务器qam verilog testbench

- FPGA云服务器qam调制verilog testbench

- FPGA云服务器调制信号verilog

- FPGA云服务器硬件工程师verilog面试题

- FPGA云服务器fsk verilog

- FPGA云服务器qam调制信号verilog

- FPGA云服务器verilog开发程序

- FPGA云服务器调制信号verilog testbench

- FPGA云服务器verilog配置

- FPGA云服务器fsk调制解调系统verilog

- FPGA云服务器verilog testbench频偏

- FPGA云服务器verilog仿真

- FPGA云服务器系统verilog包含testbench

- FPGA云服务器通信verilog

- FPGA云服务器信号模块verilog

- FPGA云服务器滤波器verilog da

- FPGA云服务器软解调verilog testbench

FPGA云服务器您可能感兴趣

- FPGA云服务器设置

- FPGA云服务器系统开发

- FPGA云服务器信道

- FPGA云服务器解调

- FPGA云服务器误码

- FPGA云服务器调制

- FPGA云服务器ask

- FPGA云服务器统计

- FPGA云服务器模块

- FPGA云服务器snr

- FPGA云服务器testbench

- FPGA云服务器matlab

- FPGA云服务器测试

- FPGA云服务器验证

- FPGA云服务器文件

- FPGA云服务器驱动

- FPGA云服务器辅助

- FPGA云服务器实验

- FPGA云服务器算法

- FPGA云服务器系统

- FPGA云服务器教程

- FPGA云服务器图像

- FPGA云服务器程序

- FPGA云服务器技术

- FPGA云服务器阿里云

- FPGA云服务器芯片

- FPGA云服务器逻辑

- FPGA云服务器开发

- FPGA云服务器结构

- FPGA云服务器信号

云服务器ECS

云服务器ECS是一种安全可靠、弹性可伸缩的IaaS级云计算服务。在这里你可以获取最新的ECS产品资讯、最前沿的技术交流以及优惠活动等信息,加速自己的技术成长。

+关注