FPGA设计8位十进制计数器异步/同步模块以及m序列码产生器模块

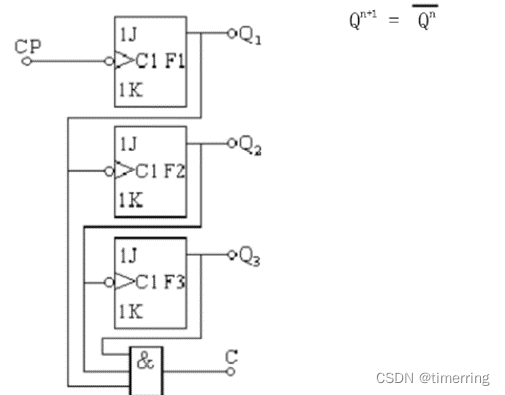

【实验三】设计一个8位十进制计数器(异步/同步)模块实验内容与原理说明根据计数器的构成原理,必须由四个触发器的状态来表示一位十进制数的四位二进制编码。而四位编码总共有十六个状态。所以必须去掉其中的六个状态,至于去掉哪六个状态,可有不同的选择。这里考虑去掉1010~1111六个状态,即采用8421BCD 码的编码方式来表示一位十进制数。在十进制运算时,当相加二数之和大于9时,便产生进位。可是用B....

FPGA设计8位异步、同步二进制计数器

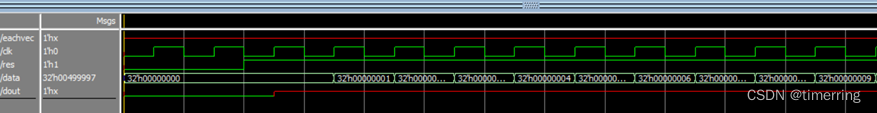

【实验要求】 实验内容与原理说明(包括框图、逻辑表达式和真值表)。实验模块程序代码(设计模块Design Block)和激励代码(激励模块Test Bench)。仿真波形图。综合得到的门级电路图。实验结果分析及思考。每一次报告用Word文档提交,文件名:姓名_班级_第几次实验_学号。【实验软件工具】QuartusII;ModelSim SE.【一】设计一个8位异步二进制计数器模块实验内...

本页面内关键词为智能算法引擎基于机器学习所生成,如有任何问题,可在页面下方点击"联系我们"与我们沟通。

FPGA云服务器您可能感兴趣

- FPGA云服务器testbench

- FPGA云服务器matlab

- FPGA云服务器设置

- FPGA云服务器系统开发

- FPGA云服务器信道

- FPGA云服务器误码

- FPGA云服务器调制解调系统

- FPGA云服务器统计

- FPGA云服务器模块

- FPGA云服务器snr

- FPGA云服务器verilog

- FPGA云服务器测试

- FPGA云服务器验证

- FPGA云服务器文件

- FPGA云服务器驱动

- FPGA云服务器调制

- FPGA云服务器辅助

- FPGA云服务器实验

- FPGA云服务器算法

- FPGA云服务器系统

- FPGA云服务器教程

- FPGA云服务器图像

- FPGA云服务器程序

- FPGA云服务器开发

- FPGA云服务器技术

- FPGA云服务器阿里云

- FPGA云服务器芯片

- FPGA云服务器逻辑

- FPGA云服务器信号

- FPGA云服务器结构

云服务器ECS

云服务器ECS是一种安全可靠、弹性可伸缩的IaaS级云计算服务。在这里你可以获取最新的ECS产品资讯、最前沿的技术交流以及优惠活动等信息,加速自己的技术成长。

+关注