【启动】芯片启动过程全解析

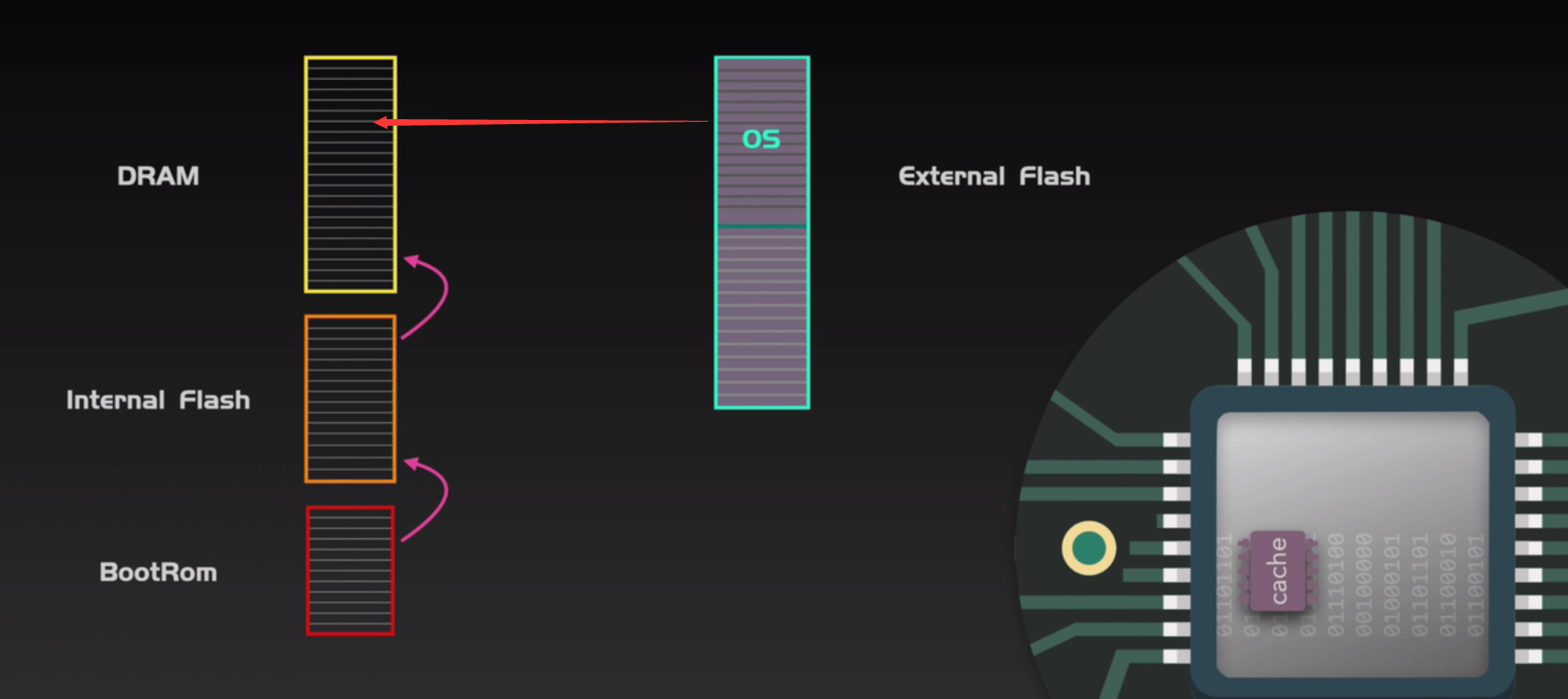

Hi!早,今天来和你一起聊聊芯片启动过程发生了什么。 内容基本来自文末推荐视频 当你按下电源开关的那一瞬间,第一行代码如何在芯片上运行起来的呢? 嵌入式软件代码需要一定的方式烧录到芯片中才能运行,除了物理刻蚀,无论是通讯端口的传输或者调试端口的烧录,都需要驱动程序...

OVP过压保护芯片:为何电子工程师需要它?功能、作用全解析

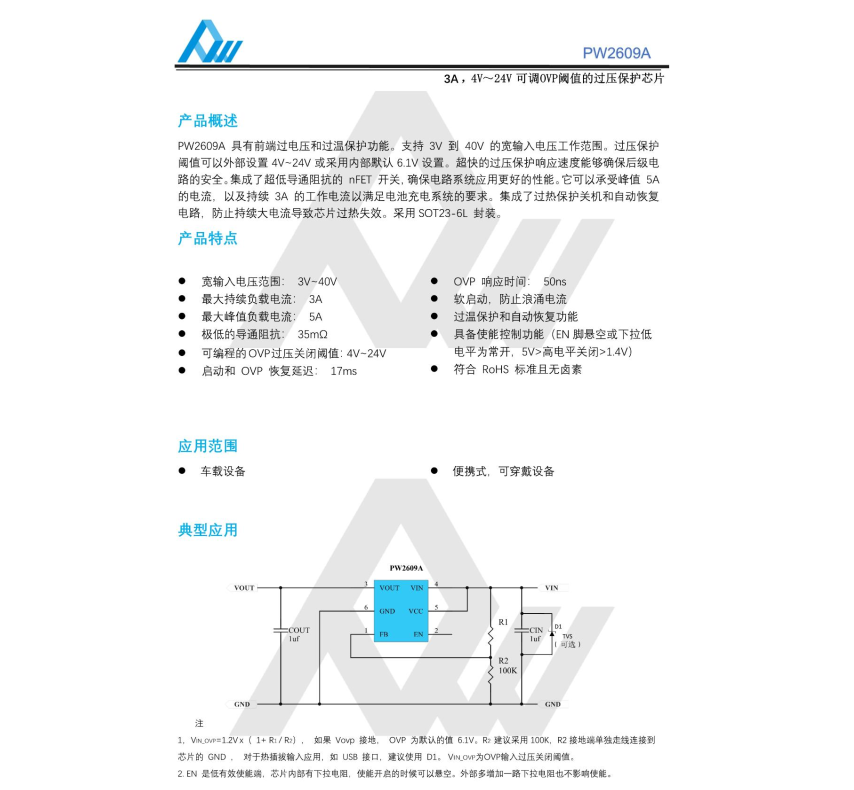

OVP 过压保护芯片OVP 过压保护 IC: 为了保护后级电路, 平芯微早早推出了系列 OVP 过压保护芯片产品, 很多客户对于 OVP 过压保护芯片的功能和使用仍然存在一些误解。 这次我们平芯微就针对 OVP 过压保护芯片功能使用做详细的描述和介绍。 首先我们需要先看下芯片规格书的描述(如下图) , 有一定了解后, 我们再往下给大家讲解。 ...

【芯片前端】“异步FIFO全解析”的BUG——格雷码连续性

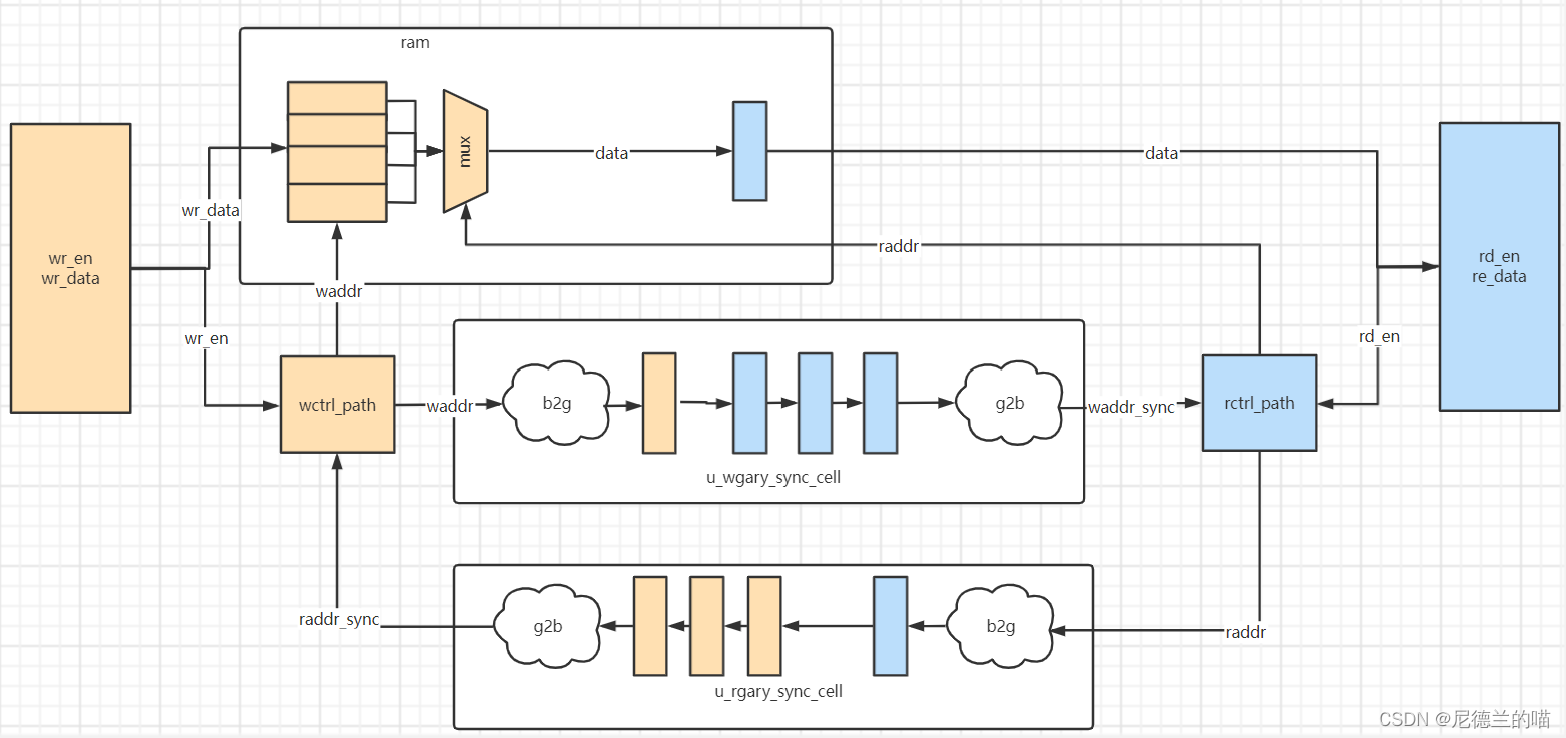

前言在前几天写完【芯片前端】保持代码手感——异步FIFO全解析之后自我感觉非常良好,觉得异步fifo的问题我已经全部拿捏了,没想到今天突然想到一个我自己代码里的bug。代码中的BUG事情的源头在同步fifo里,深度任意可配的同步fifo里使用了两个非饱和的cnt计数器记录读写地址指针,waddr和raddr均比实际地址多一位,最高位用来指示套圈情况。当waddr和raddr的最高位相同时,fif....

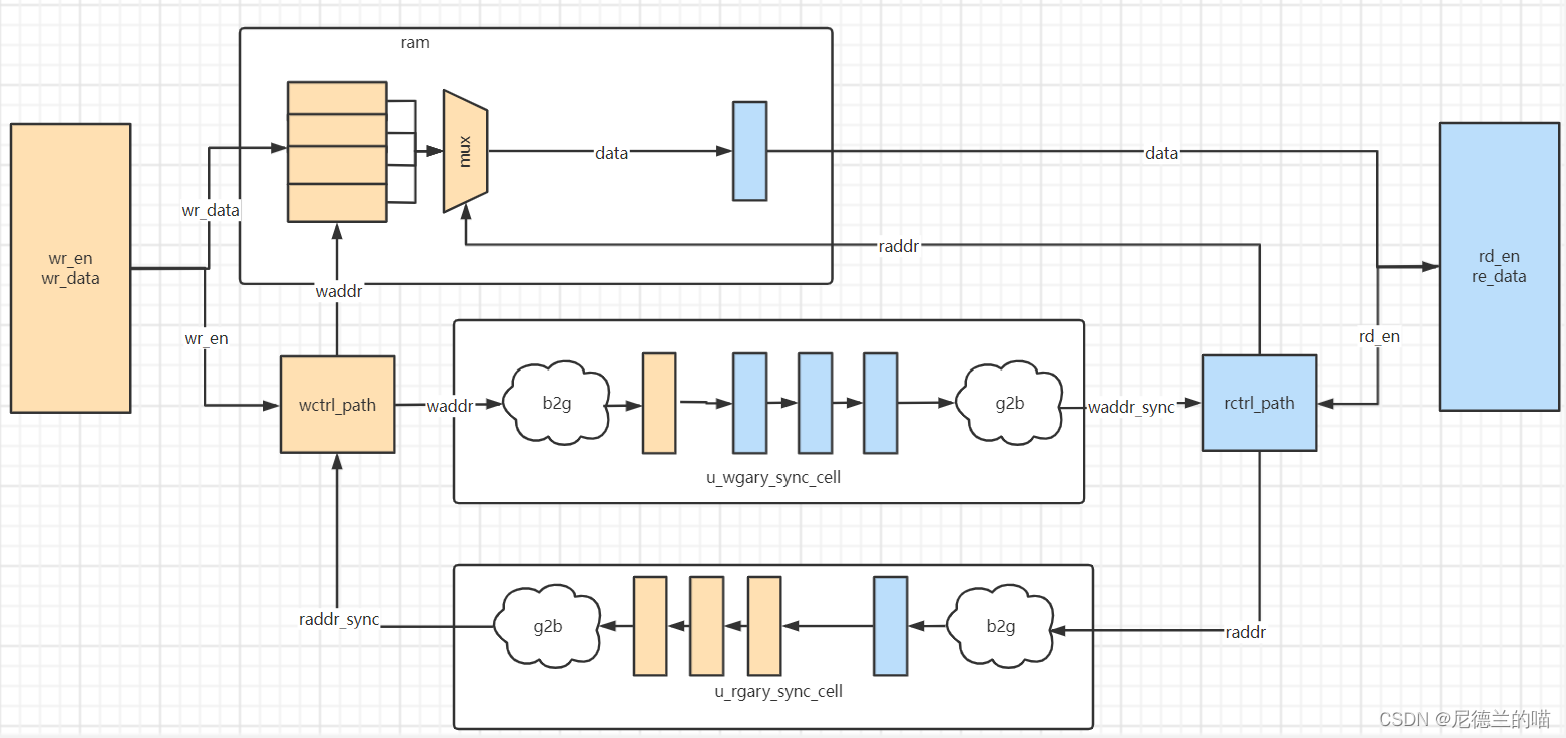

【芯片前端】保持代码手感——异步FIFO全解析

前言关于FIFO和异步处理我已经写过很多东西了:进阶之路——二进制与格雷码的相互转换模块设计【异步FIFO的一些小事·0】异步FIFO同步化设计【异步FIFO的一些小事·1】空满判断与格雷码【异步FIFO的一些小事·2】异步FIFO中异步走线延时约束的一些思考【异步FIFO的一些小事·3】异步FIFO中指针走线延时的一些思考【异步电路碎碎念5】 —— 跨异步处理的几个注意事项【芯片前端】保持代码....

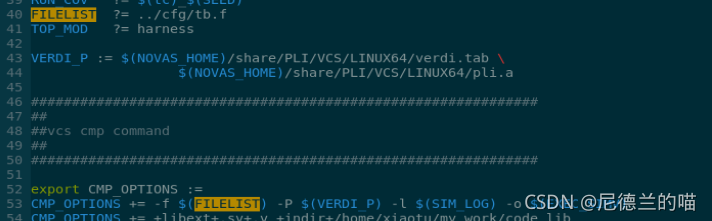

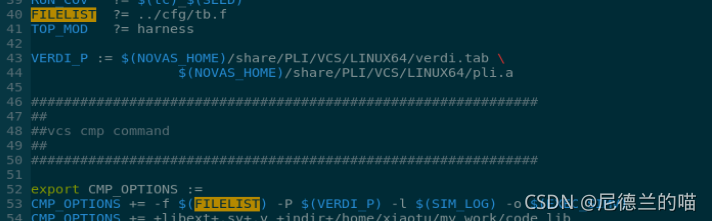

【芯片前端】Filelist -f/-F的文件解析方式探究

前言测试所用的文件目录(列举关键文件):/home/xiaotu/my_work/uvm_demo -cfg/ -ctl/ -rtl/ -sim/ -Makefile -tc/ -th/ -ver/-f/-F影响后跟filelist文件内的解析方式,不影响后跟文件的解析方式典型的场景,就是makefile里用-f还是-F来后缀路径都是一样的(仅仅对于解析这个list) ,绝对路径就按绝对...

【芯片前端】Filelist -f/-F的文件解析方式探究

前言测试所用的文件目录(列举关键文件):1. /home/xiaotu/my_work/uvm_demo 2. -cfg/ 3. -ctl/ 4. -rtl/ 5. -sim/ 6. -Makefile 7. -tc/ 8. -th/ 9. -ver/-f/-F影响后跟filelist文件内的解析方式,不影响后跟文件的解析方式典型的场景,就是makefile里用-f还是-F来后缀路径都是...

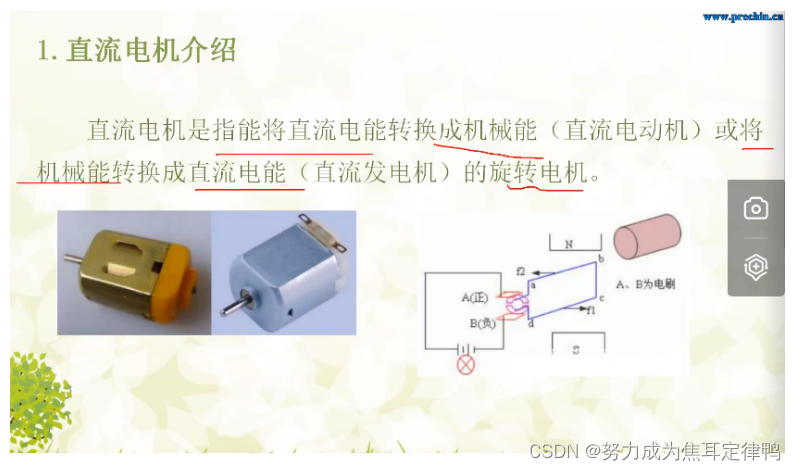

单片机:直流电机(内含ULN2003芯片,硬件原理及解析,软件编程及注释)

注:1-7引脚分别对应的16-10引脚依次为7个输入输出,中间依次用非门连接。如1号引脚输入端输入为0,为假,16脚输出为1,为真,若VCC连接24V,则输出为24V8脚为GND9脚为VCC以下此种方式连接直流电机是错误的!因为输出无法直接输出高电平,输出的均为低电平,只有在1和16脚对应连接时才为一端为高电平,一端为低电平(外部连接上拉电阻可以实现某一管脚为高电平)连接直流电机正确方法VCC端....

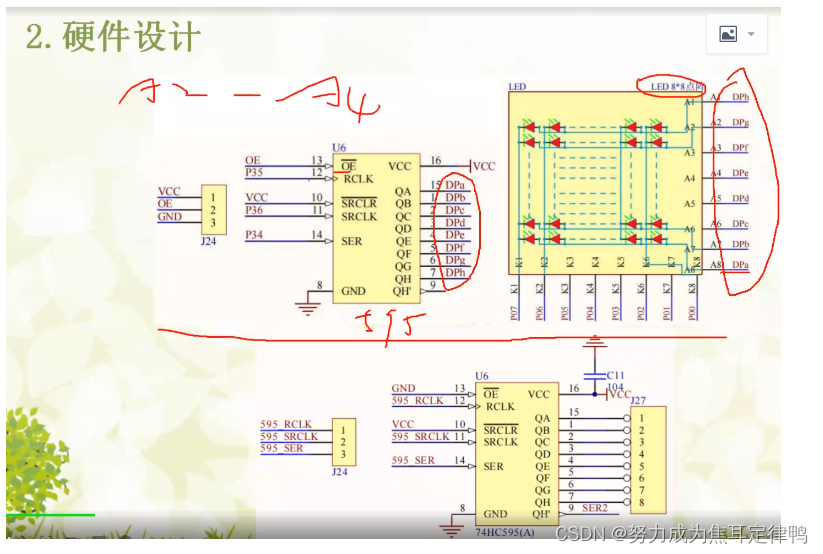

74HC595芯片的IO扩展(串转并)实验(包含硬件原理和软件编程解析和代码)

#include"reg52.h" typedef unsigned char u8; typedef unsigned int u16; //特殊管脚寄存器的对应一般不可变 sbit rCLK=P3^5;//移位寄存器时钟输入---注:RCLK已被reg52.h定义使用,需要重新定义 sbit SRCLK=P3^6;//存储寄存器时钟输入 sbit SER=P3^4;//串行数据输入 #def....

【直播预告】平头哥芯片开放社区(OCC)合作伙伴计划即1520计划全解析

直播预告:在需求极度碎片化的AIoT时代,应用开发面临着芯片选型难、应用方案移植成本高、复用性低等痛点。平头哥芯片开放社区(OCC)基于“1天上手、5天出原型、20天出产品”的理念及标准,依托平头哥全栈技术能力,聚合芯片、算法、应用、智能硬件等产业链合作伙伴,共同构建AIoT芯片生态,通过芯片抽象打造通用的应用开发平台,提高应用方案的复用性,加速产品创新及落地能力,推动AIoT行业快速发展。 直....

本页面内关键词为智能算法引擎基于机器学习所生成,如有任何问题,可在页面下方点击"联系我们"与我们沟通。

云解析DNS您可能感兴趣

- 云解析DNS迈向

- 云解析DNS智能

- 云解析DNS可视化

- 云解析DNS神经网络

- 云解析DNS数学

- 云解析DNS网络

- 云解析DNS原理

- 云解析DNS洞察

- 云解析DNS评论

- 云解析DNS api接口

- 云解析DNS域名

- 云解析DNS源码

- 云解析DNS java

- 云解析DNS阿里云

- 云解析DNS解析

- 云解析DNS服务器

- 云解析DNS dns

- 云解析DNS应用

- 云解析DNS json

- 云解析DNS备案

- 云解析DNS配置

- 云解析DNS网站

- 云解析DNS数据

- 云解析DNS ip

- 云解析DNS linux

- 云解析DNS访问

- 云解析DNS设置

- 云解析DNS xml

- 云解析DNS android

- 云解析DNS python