PCIe 参考时钟架构 (Refclk Architecture)

开聊之前先梳理几个概念: Jitter,时钟抖动,是对于同一 Clock 而言的, 是时钟源引起的,用来描述被测时钟与理想时钟在时域的偏差(单位为 ps RMS,皮秒均方根)。 Skew,时钟偏斜,是对于多个时钟线而言的,是时钟树不平衡引起的。 此外还有一个概念是频率稳定性,用来描述被测时钟频率与理想时钟频率的偏差(单....

FPGA - 7系列 FPGA内部结构之Clocking -01- 时钟架构概述(二)

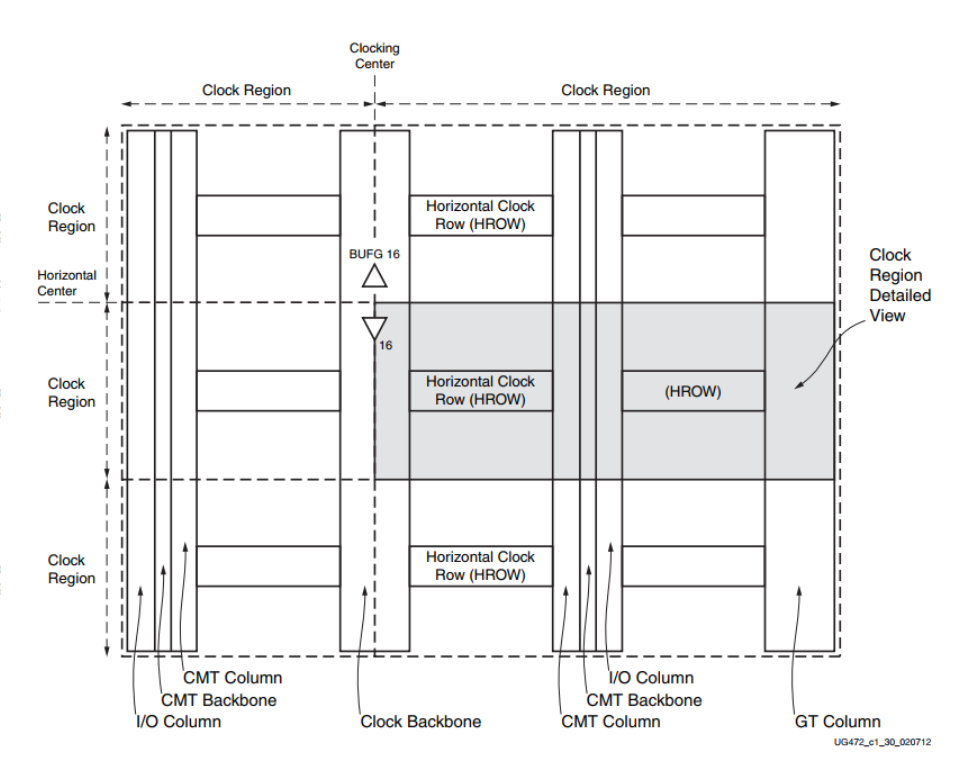

7 系列 FPGA 时钟与前几代 FPGA 的区别尽管所有 7 系列器件具有相同的基本架构,但家族之间和家族内的器件之间存在一些架构差异。每个 7 系列 FPGA 在器件的左边缘至少有一个完整的 I/O 列。 GT 可以是 7 系列 FPGA(GTP、GTX 或 GTH)支持的任何一种串行收发器。带有 GT 的设备要么在设备的右边缘有混合的 GT 和 I/O 列(一些 Kintex-7 设备和一....

FPGA - 7系列 FPGA内部结构之Clocking -01- 时钟架构概述(一)

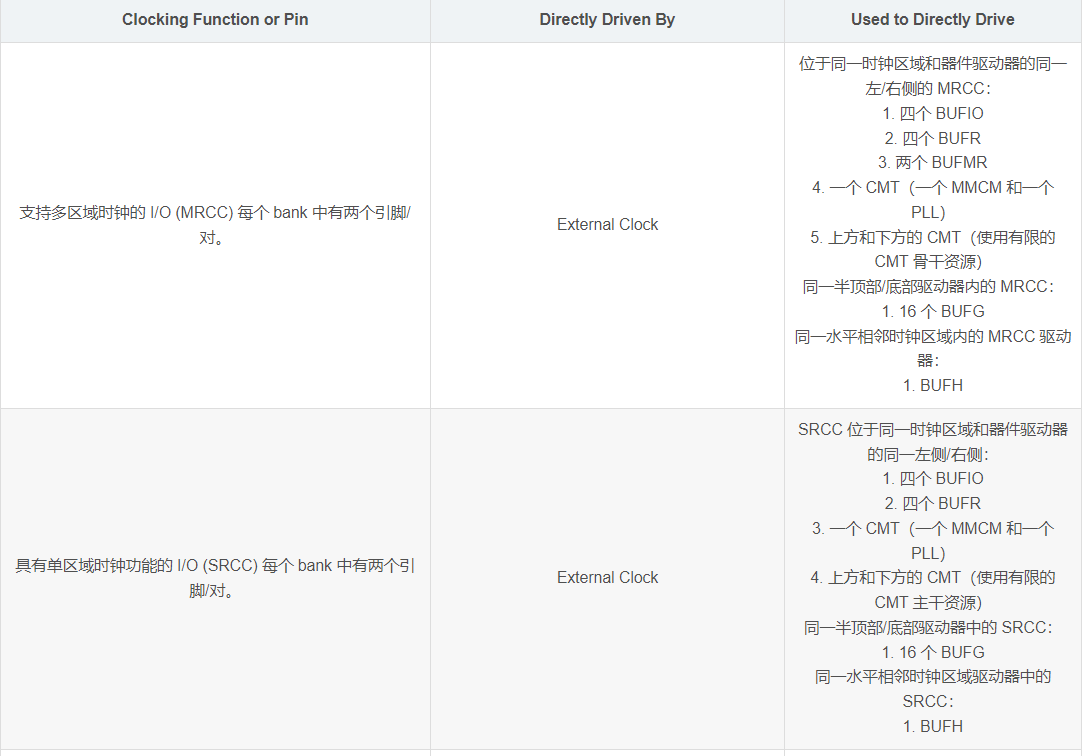

前言本文节选UG472的第一章,进行整理翻译,主要用于介绍7系列的FPGA的时钟架构以及与前几代的FPGA的区别,并总结了时钟连接的相关使用方法。时钟架构概述7 系列 FPGA 时钟资源通过专用的全局和区域 I/O 和时钟资源管理复杂和简单的时钟要求。 时钟管理块 (CMT) 提供时钟频率合成、去偏斜和抖动过滤功能。在设计时钟功能时,不建议使用非时钟资源,例如本地布线。全局时钟树允许跨器件同步元....

本页面内关键词为智能算法引擎基于机器学习所生成,如有任何问题,可在页面下方点击"联系我们"与我们沟通。

金融级分布式架构

SOFAStack™(Scalable Open Financial Architecture Stack)是一套用于快速构建金融级分布式架构的中间件,也是在金融场景里锤炼出来的最佳实践。

+关注