计算机组成原理(7)----CPU内部单总线数据通路

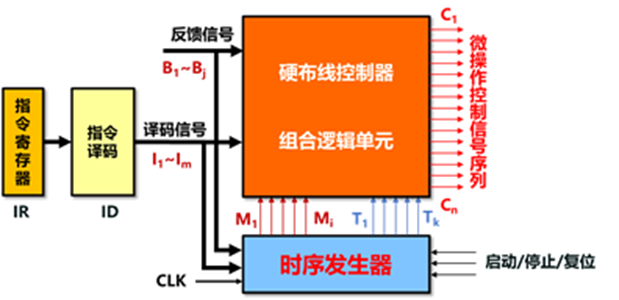

1.CPU内部单总线方式 单总线方式如下图所示,寄存器的控制信号,例如 等,都是由CU发出的。 ...

【头歌·计组·自己动手画CPU】五、单总线CPU设计(理论版) 【计算机硬件系统设计】

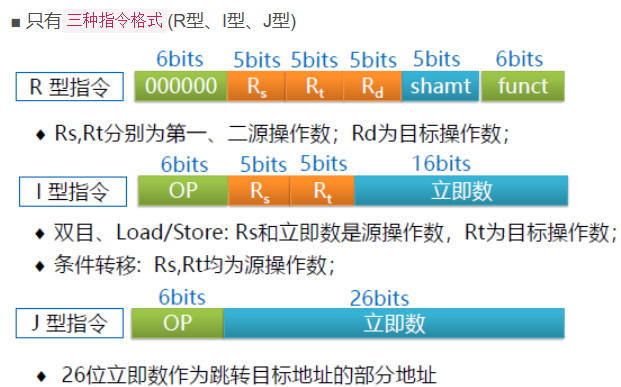

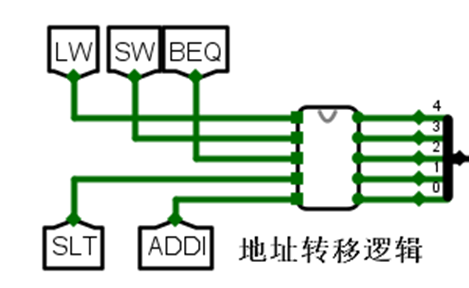

欢迎 ❤️关注 点赞 收藏 ✍️留言 一、课程设计目的 利用经典的单总线结构运行MIPS程序,可以设计传统三级时序硬布线控制器,也可以设计现代时序硬布线控制器和微程序控制器,可以为不同的时序系统增加中断处理机制。 二、课程设计内容 单总线CPU设计(定长指令周期3级时序)(HUST) MIPS指令译码器设计 1.1.实验目的...

【自己动手画CPU】单总线CPU设计(三)

⏰诗赋清音:云生高巅梦远游, 星光点缀碧海愁。 山川深邃情难晤, 剑气凌云志自修。 1. 闯关目的 第1关:MIPS指令译码器设计 (1) 理解指令译码的基本概念; (2) 将32位MIPS指令字译码成不同的指令译码信号。 第2关:单总线CPU微程序入口查找逻辑 (1) 理解微程序控制器中微程序分支的基本原理; (2) 设计实现微程序入口查...

【自己动手画CPU】单总线CPU设计(二)

1. 闯关目的 第1关:MIPS指令译码器设计 (1) 理解指令译码的基本概念; (2) 将32位MIPS指令字译码成不同的指令译码信号。 第2关:变长指令周期---时序发生器FSM设计 (1) 理解传统三级时序系统中时序发生器的基本原理; (2) 设计实现变长指令周期的时序发生器状态机以及输出函数。 第3关:变长指令周期---时序发生器输...

【自己动手画CPU】单总线CPU设计(一)

⏰诗赋清音:云生高巅梦远游, 星光点缀碧海愁。 山川深邃情难晤, 剑气凌云志自修。 1. 闯关目的 第1关:MIPS指令译码器设计 (1) 理解指令译码的基本概念; (2) 将32位MIPS指令字译码成不同的指令译码信号。 第2关:定长指令周期---时序发生器FSM设计...

CPU的单总线和双总线

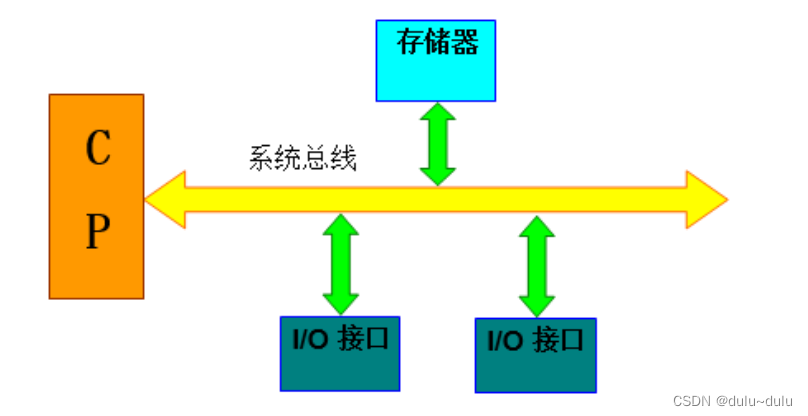

总线分类(一)CPU按照总线的功能分可分为1.数据总线数据总线是CPU与存储器、CPU与I/O接口设备之间传送数据信息(各种指令数据信息)的总线,这些信号通过数据总线往返于CPU与存储器、CPU与I/O接口设备之间,因此,数据总线上的信息是双向传输的。2.地址总线地址总线上传送的是CPU向存储器、I/O接口设备发出的地址信息,寻址能力是CPU特有的功能,地址总线上传送的地址信息仅由CPU发出,因....

本页面内关键词为智能算法引擎基于机器学习所生成,如有任何问题,可在页面下方点击"联系我们"与我们沟通。